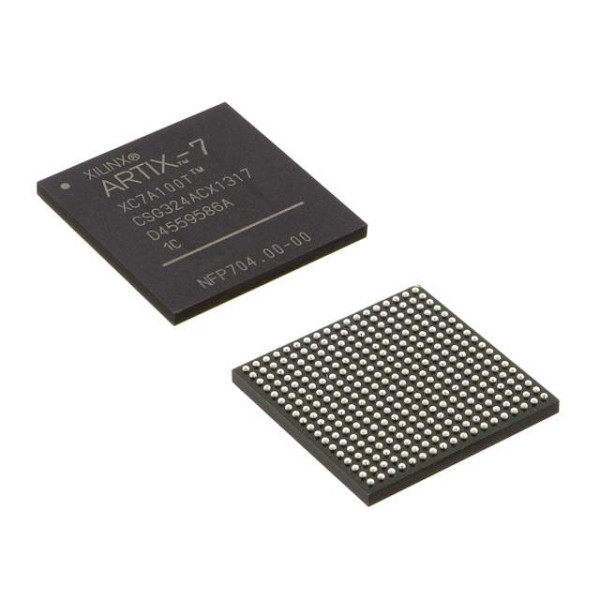

XC7A50T-2CSG324I FPGA – Veldprogrammeerbare Hek-skikking XC7A50T-2CSG324I

♠ Produkbeskrywing

| Produkkenmerk | Attribuutwaarde |

| Vervaardiger: | Xilinx |

| Produkkategorie: | FPGA - Veldprogrammeerbare Hek-skikking |

| Reeks: | XC7A50T |

| Aantal logiese elemente: | 52160 LE |

| Aantal I/O's: | 210 I/O |

| Toevoerspanning - Min: | 0.95 V |

| Toevoerspanning - Maks: | 1.05 V |

| Minimum bedryfstemperatuur: | - 40 grade Celsius |

| Maksimum bedryfstemperatuur: | + 100°C |

| Datatempo: | - |

| Aantal senders/ontvangers: | - |

| Monteringstyl: | SMD/SMT |

| Pakket / Doos: | CSBGA-324 |

| Handelsmerk: | Xilinx |

| Verspreide RAM: | 600 kbit |

| Ingeboude Blok RAM - EBR: | 2700 kbit |

| Voggevoelig: | Ja |

| Aantal logiese skikkingsblokke - LAB's: | 4075 LAB |

| Bedryfsvoorsieningsspanning: | 1 V |

| Produk Tipe: | FPGA - Veldprogrammeerbare Hek-skikking |

| Fabriekspakhoeveelheid: | 1 |

| Subkategorie: | Programmeerbare Logika-IC's |

| Handelsnaam: | Artix |

| Eenheidsgewig: | 1 ons |

♠ Xilinx® 7-reeks FPGA's bestaan uit vier FPGA-families wat die volledige reeks stelselvereistes aanspreek, wat wissel van lae koste, klein vormfaktor, koste-sensitiewe, hoë-volume toepassings tot ultra-hoë-end konnektiwiteitsbandwydte, logikakapasiteit en seinverwerkingsvermoë vir die mees veeleisende hoëprestasie-toepassings.

Xilinx® 7-reeks FPGA's bestaan uit vier FPGA-families wat die volledige reeks stelselvereistes aanspreek, wat wissel van lae koste, klein vormfaktor, koste-sensitiewe, hoë-volume toepassings tot ultra-hoë-end konnektiwiteitsbandwydte, logikakapasiteit en seinverwerkingsvermoë vir die mees veeleisende hoëprestasie-toepassings. Die 7-reeks FPGA's sluit in:

• Spartan®-7-familie: Geoptimaliseer vir lae koste, laagste krag en hoë I/O-werkverrigting. Beskikbaar in laekoste, baie klein vormfaktorverpakking vir die kleinste PCB-voetspoor.

• Artix®-7-familie: Geoptimaliseer vir lae-krag toepassings wat seriële transceivers en hoë DSP- en logika-deurset vereis. Verskaf die laagste totale materiaalkoste vir hoë-deurset, koste-sensitiewe toepassings.

• Kintex®-7-familie: Geoptimaliseer vir die beste prys-prestasie met 'n 2X-verbetering in vergelyking met die vorige generasie, wat 'n nuwe klas FPGA's moontlik maak.

• Virtex®-7-familie: Geoptimaliseer vir die hoogste stelselprestasie en kapasiteit met 'n 2x verbetering in stelselprestasie. Toestelle met die hoogste vermoë word moontlik gemaak deur gestapelde silikon-interkonneksie (SSI)-tegnologie.

Gebou op 'n moderne, hoëprestasie-, lae-krag (HPL), 28 nm, hoë-k metaalhek (HKMG) prosestegnologie, maak 7-reeks FPGA's 'n ongeëwenaarde toename in stelselprestasie moontlik met 2.9 Tb/s I/O-bandwydte, 2 miljoen logikaselkapasiteit en 5.3 TMAC/s DSP, terwyl hulle 50% minder krag verbruik as vorige generasie toestelle om 'n volledig programmeerbare alternatief vir ASSP's en ASIC's te bied.

• Gevorderde hoëprestasie FPGA-logika gebaseer op werklike 6-invoer-opsoektabel (LUT)-tegnologie wat as verspreide geheue konfigureerbaar is.

• 36 Kb dubbelpoort-blok-RAM met ingeboude FIFO-logika vir databuffering op die skyfie.

• Hoëprestasie SelectIO™-tegnologie met ondersteuning vir DDR3-koppelvlakke tot 1 866 Mb/s.

• Hoëspoed-seriële konnektiwiteit met ingeboude multi-gigabit-senders en -ontvangers van 600 Mb/s tot maksimum snelhede van 6.6 Gb/s tot 28.05 Gb/s, wat 'n spesiale lae-kragmodus bied, geoptimaliseer vir skyfie-tot-skyfie-koppelvlakke.

• ’n Gebruiker-konfigureerbare analoog-koppelvlak (XADC), wat dubbele 12-bis 1MSPS analoog-na-digitaal-omsetters met ingeboude termiese en toevoersensors insluit.

• DSP-skyfies met 25 x 18 vermenigvuldiger, 48-bis akkumulator en voor-toevoeging vir hoëprestasie-filtering, insluitend geoptimaliseerde simmetriese koëffisiëntfiltering.

• Kragtige klokbestuurteëls (CMT), wat fasegeslote lus (PLL) en gemengde-modus klokbestuurder (MMCM) blokke kombineer vir hoë presisie en lae jitter.

• Implementeer vinnig ingebedde verwerking met MicroBlaze™-verwerker.

• Geïntegreerde blok vir PCI Express® (PCIe), vir tot x8 Gen3-eindpunt- en wortelpoortontwerpe.

• Wye verskeidenheid konfigurasie-opsies, insluitend ondersteuning vir kommoditeitsgeheue, 256-bis AES-enkripsie met HMAC/SHA-256-verifikasie, en ingeboude SEU-opsporing en -korreksie.

• Laekoste, draadgebonde, kaal-die flip-chip, en hoë seinintegriteit flip-chip verpakking bied maklike migrasie tussen familielede in dieselfde pakket. Alle pakkette is beskikbaar in Pb-vrye en geselekteerde pakkette in Pb-opsie.

• Ontwerp vir hoë werkverrigting en laagste krag met 28 nm, HKMG, HPL-proses, 1.0V kernspanningsprosestegnologie en 0.9V kernspanningsopsie vir selfs laer krag.